# Working Draft American National Standard

# T10 Project 1302D

Revision 67 133-May June-99

# Information technology - SCSI Parallel Interface-3 (SPI-3)

This is a draft proposed American National Standard of Accredited Standards Committee NCITS. As such this is not a completed standard. The T10 Technical Committee may modify this document as a result of comments received during public review and its approval as a standard. Use of the information contained here in is at your own risk.

Permission is granted to members of NCITS, its technical committees, and their associated task groups to reproduce this document for the purposes of NCITS standardization activities without further permission, provided this notice is included. All other rights are reserved. Any commercial or for-profit duplication is strictly prohibited.

T10 Technical Editor: George O. Penokie

IBM MS 2B7

3605 Highway 52 N. Rochester, MN 55901

**USA**

Telephone: 507-253-5208 Facsimile: 507-253-2880 Email: gop@us.ibm.com

Reference number ISO/IEC \*\*\*\*\*\*: 199x ANSI NCITS. - 199x

# POINTS OF CONTACT:

T10 Chair

John B. Lohmeyer

T10 Vice-Chair

George O. Penokie

LSI IBM

4420 ArrowsWest Drive 3605 Highway 52 N. MS 2B7

Colo Spgs, CO 80907-3444

Rochester, MN 55901

Tel: (719) 533-7560

Tel: (507) 253-5208

Fax: (719) 593-7036

Fax: (507) 253-2880

Email: lohmeyer@ix.netcom.com

Email: gop@us.ibm.com

**NCITS Secretariat**

NCITS Secretariat Telephone: 202-737-8888 1250 Eye Street, NW Suite 200 Facsimile: 202-638-4922 Washington, DC 20005 Email: ncits@itic.org

T10 Reflector Internet address for subscription to the T10 reflector: majordomo@symbios.com

The message body should be: subscribe t10

Internet address for distribution via T10 reflector: T10@symbios.com

**Document Distribution**

Global Engineering Telephone: 303-792-2181 or 15 Inverness Way East 800-854-7179 Englewood, CO 80112-5704 Facsimile: 303-792-2192

#### **ABSTRACT**

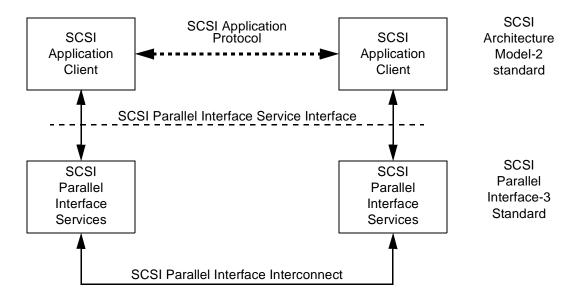

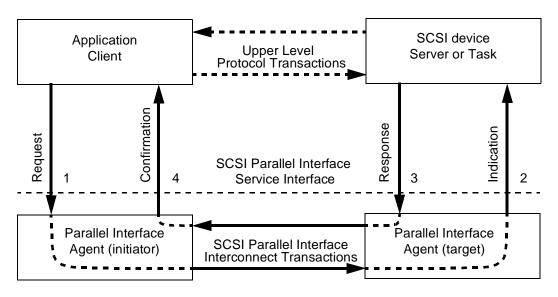

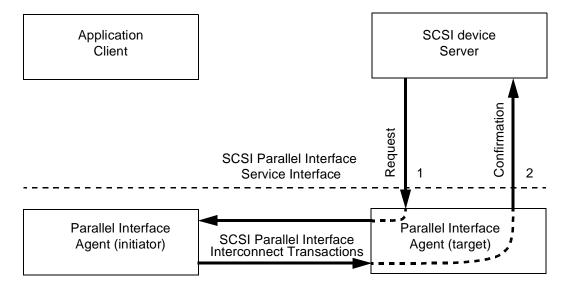

This standard defines mechanical, electrical, timing requirements, command, and the task management delivery protocol requirements to transfer commands and data between SCSI devices attached to a SCSI parallel interface. This standard is intended to be used in conjunction with the SCSI command sets. The resulting interface facilitates the interconnection of computers and intelligent peripherals and thus provides a common interface standard for both system integrators and suppliers of intelligent peripherals.

#### PATENT STATEMENT

**CAUTION:** The developers of this standard have requested that holders of patents that may be required for the implementation of the standard, disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this standard. As of the date of publication of this standard, following calls for the identification of patents that may be required for the implementation of the standard, notice of one or more claims has been received.

By publication of this standard, no position is taken with respect to the validity of this claim or of any rights in connection therewith. The known patent holder has, however, filed a statement of willingness to grant a license under these rights on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Details may be obtained from the publisher.

No further patent search is conducted by the developer or the publisher in respect to any standard it processes. No representation is made or implied that licenses are not required to avoid infringement in the use of this standard.

# **Contents**

|                                                        | Page  |

|--------------------------------------------------------|-------|

| Foreword                                               |       |

| Introduction                                           | xviii |

| 1 Scope                                                | 1     |

| Т Осоро                                                |       |

| 2 Normative references                                 | 3     |

| 2.1 Normative references                               | 3     |

| 2.2 Approved references                                | 3     |

| 2.3 References under development                       | 4     |

| 2.4 Other references                                   | 4     |

| 3 Definitions, symbols, abbreviations, and conventions | 4     |

| 3.1 Definitions                                        |       |

| 3.2 Symbols and abbreviations                          |       |

| 3.3 Keywords                                           |       |

| 3.4 Conventions                                        |       |

| 3.5 Notation for Procedures and Functions              |       |

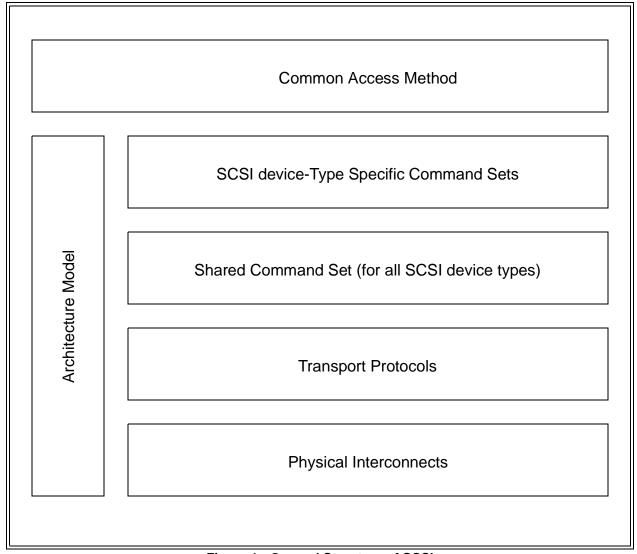

| 4 General                                              | 13    |

| 4.0.1 Data transfer modes                              |       |

| 4.1 Cables, Connectors, Signals, Transceivers          |       |

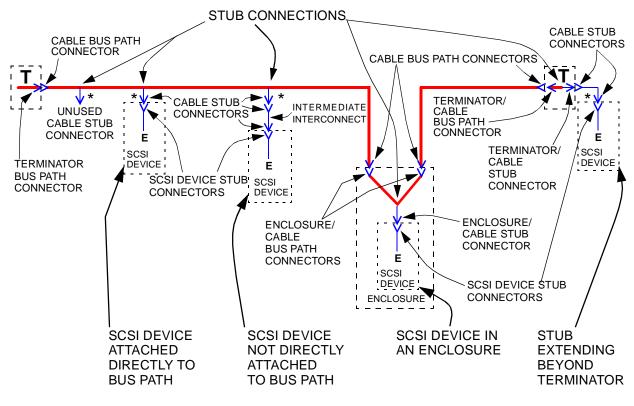

| 4.2 Physical architecture of bus                       |       |

| 4.3 Physical topology details and definitions          |       |

| 4.4 Bus loading                                        |       |

| 4.5 Termination requirements                           |       |

| 4.6 SCSI device Addressing                             |       |

| 4.7 Data transfers                                     |       |

| 4.8 Data transfer modes                                |       |

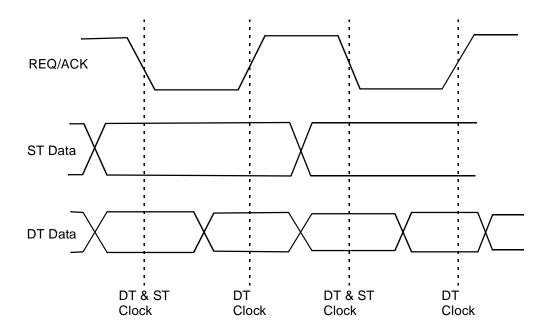

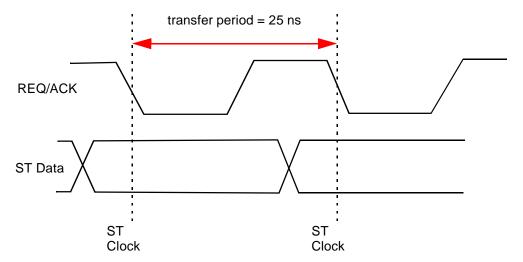

| 4.8.1 ST DATA phase parallel transfers                 | 20    |

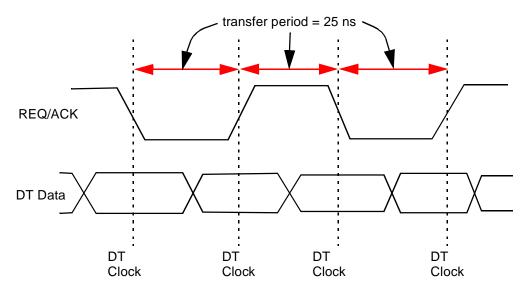

| 4.8.2 DT DATA phase parallel transfers                 | 20    |

| 4.8.2.1 Data group transfers                           | 21    |

| 4.8.2.2 Information unit transfers                     | 21    |

| 4.9 Protocol                                           | 21    |

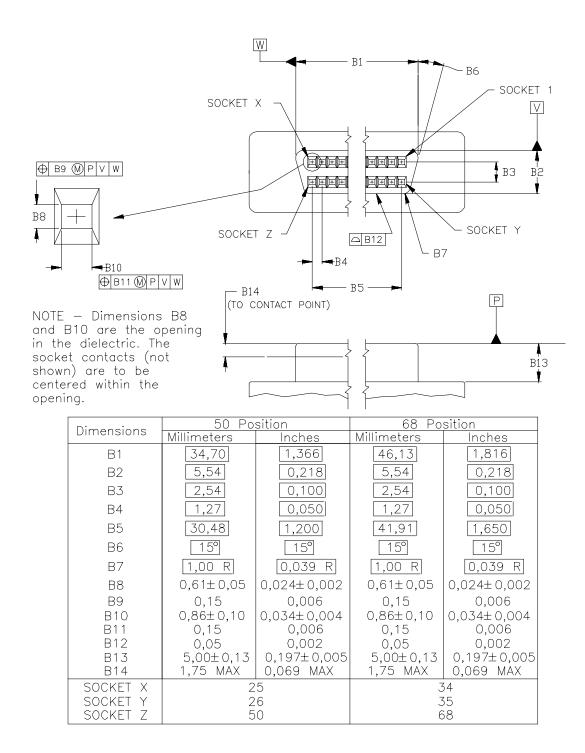

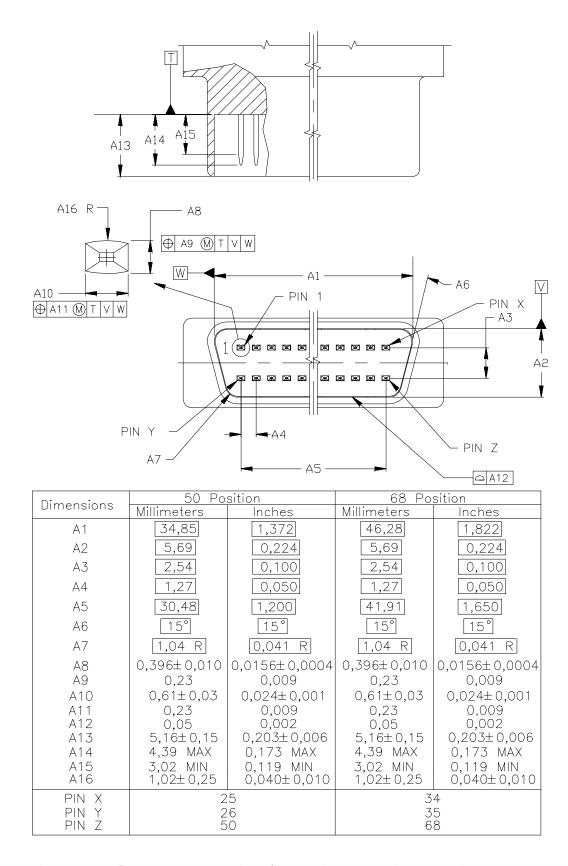

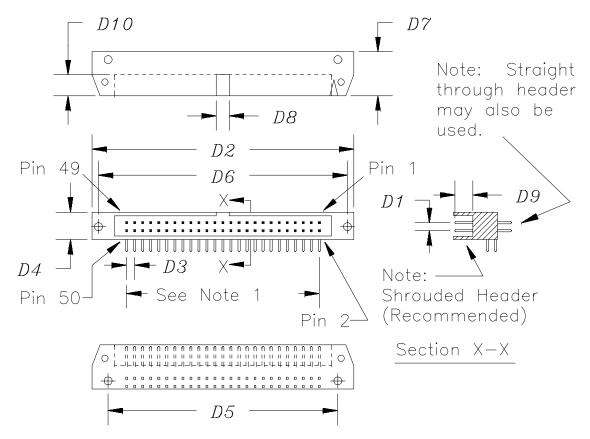

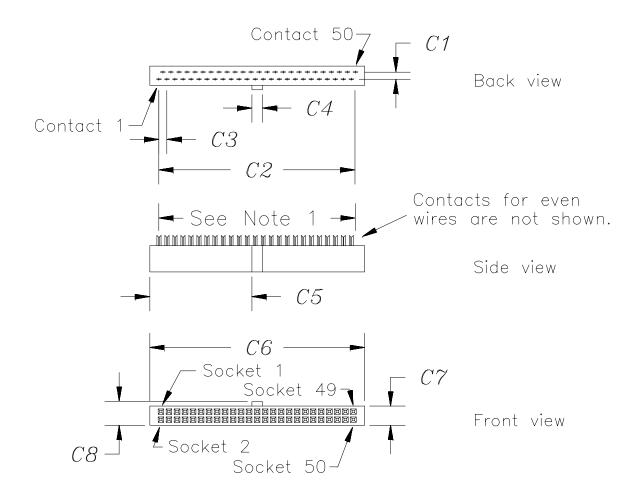

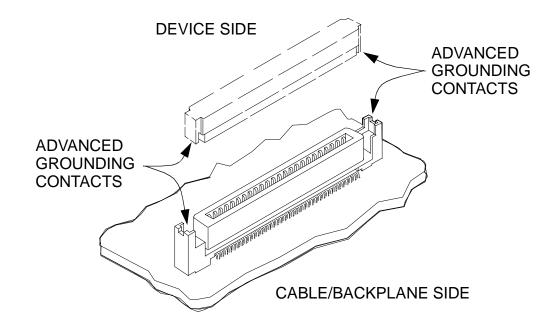

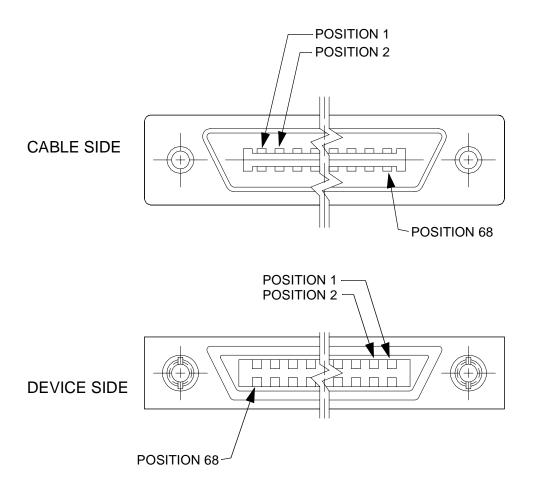

| 5 SCSI parallel interface connectors                   | 25    |

| 5.1 SCSI parallel interface connectors overview        |       |

| 5.2 Nonshielded connector                              |       |

| 5.2.1 Nonshielded connector alternative 1 - A cable    |       |

| 5.2.2 Nonshielded connector alternative 2 - A cable    |       |

| 5.2.3 Nonshielded connector alternative 3 - P cable    | 26    |

| 5.2.4 Nonshielded connector alternative 4              | 26    |

| 5.3 Shielded connector                                 |       |

| 5.3.1 Shielded connector alternative 1 - A cable       | 32    |

| 5.3.2 Shielded connector alternative 2 - A cable       | 32    |

| 5.3.3 Shielded connector alternative 3 - P cable       |       |

| 5.3.4 Shielded connector alternative 4 - P cable       |       |

| 5.4 Connector contact assignments                      |       |

| 5.4.1 SE assignments                                   |       |

| 5.4.2 Differential connector contact assignments       | 45    |

| 6 SCSI bus interconnect                                | 48    |

| 6.1 SCSI bus interconnect overview                     | 48    |

| 6.2 SCSI bus cables                                    |       |

| 6.3 Interconnect characteristics for signals           |       |

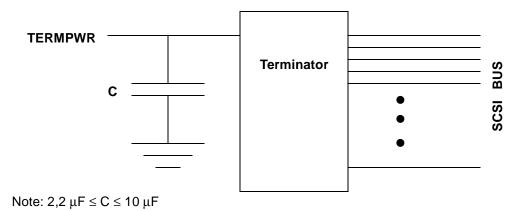

| 6.4 Decoupling characteristics for TERMPWR lines       |       |

| 6.5 Connection requirements for RESERVED lines                  |    |

|-----------------------------------------------------------------|----|

| 6.6 Cables used with SE transceivers                            |    |

| 6.6.1 SE ground offset                                          |    |

| 6.7 Cables used with LVD transceivers                           |    |

| 6.7.1 LVD stub length and spacing                               | 53 |

| 7 SCSI parallel interface electrical characteristics            | 54 |

| 7.1 SCSI parallel interface electrical characteristics overview |    |

| 7.2 SE alternative                                              |    |

| 7.2.1 SE termination                                            |    |

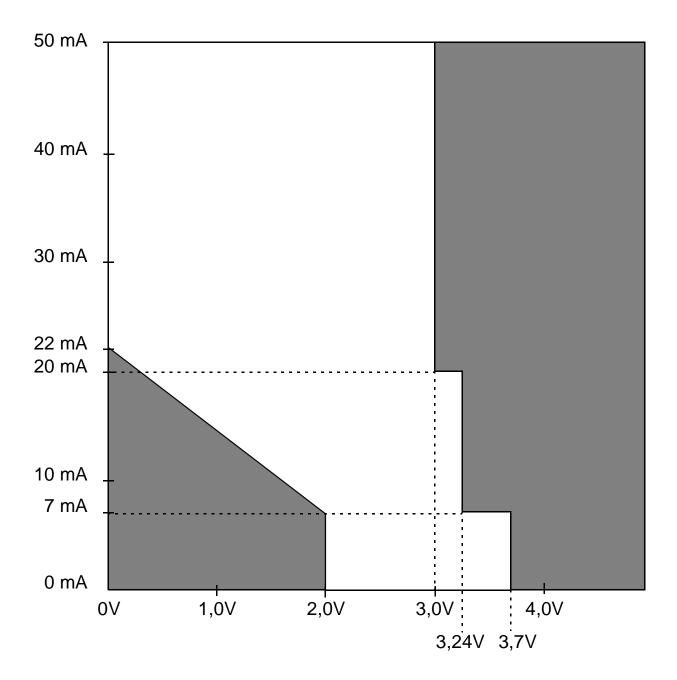

| 7.2.2 SE output characteristics                                 |    |

| 7.2.3 SE input characteristics                                  |    |

| 7.2.4 SE input and output characteristics                       |    |

| 7.3 LVD alternative                                             |    |

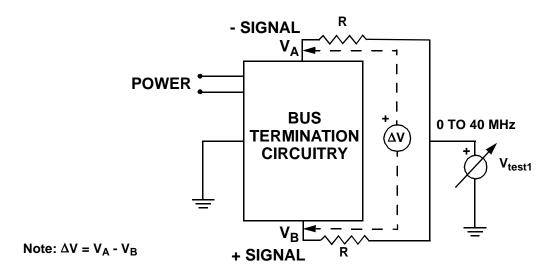

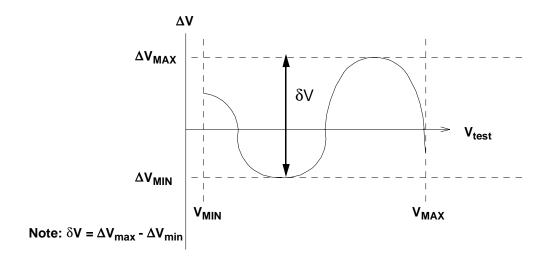

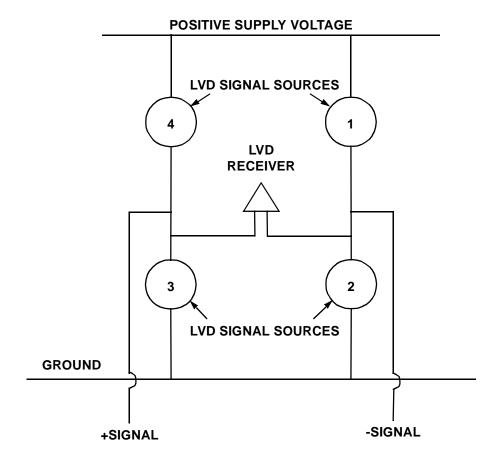

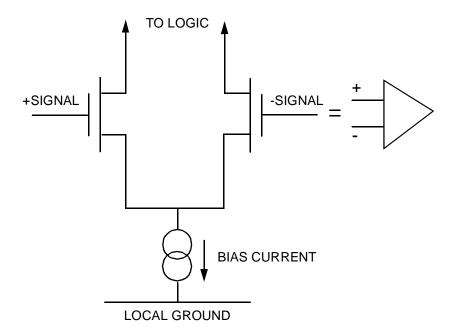

| 7.3.1 LVD termination                                           | 60 |

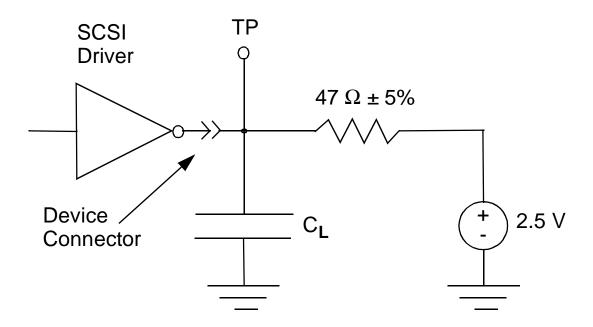

| 7.3.2 LVD driver characteristics                                | 64 |

| 7.3.3 LVD receiver characteristics                              |    |

| 7.3.4 LVD capacitive loads                                      |    |

| 7.3.4.1 Management of LVD release glitches                      |    |

| 7.3.5 SE/HVD transmission mode detection                        |    |

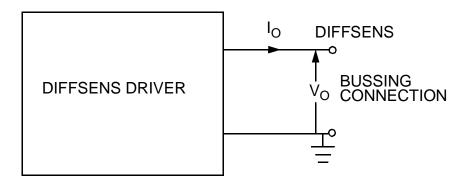

| 7.3.5.1 LVD DIFFSENS driver                                     |    |

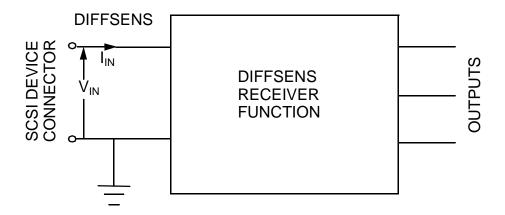

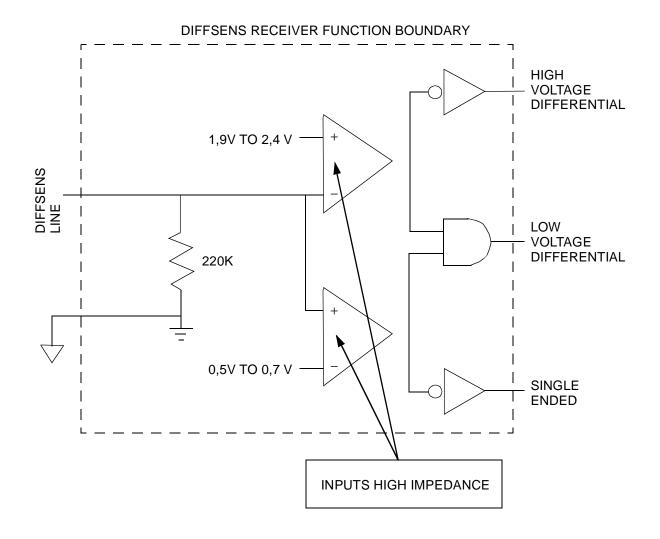

| 7.3.5.2 LVD DIFFSENS receiver                                   |    |

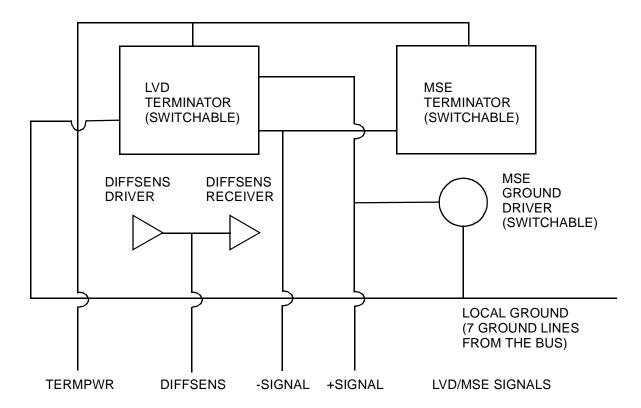

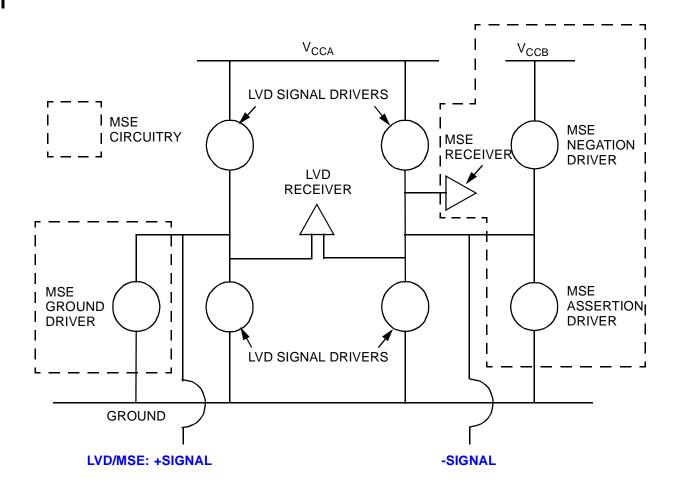

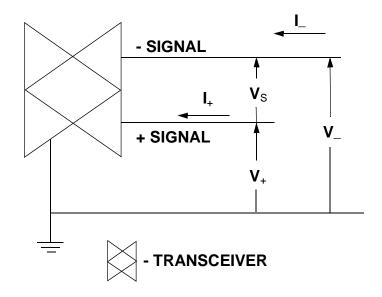

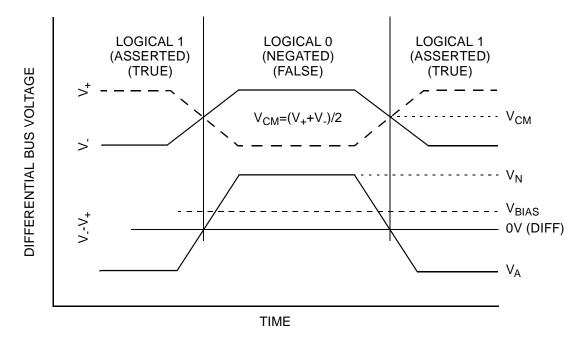

| 7.4 LVD/MSE multimode alternative                               |    |

| 7.4.1 LVD/MSE multimode termination                             |    |

| 7.4.2 LVD/MSE multimode transceiver characteristics             |    |

| 7.4.3 Ground drivers                                            |    |

| 7.5 Terminator power                                            | 75 |

| 8 SCSI bus signals                                              | 77 |

| 8.1 SCSI bus signals overview                                   |    |

| 8.2 Signal descriptions                                         |    |

| 8.3 Requirements for DB(P1) during DT data transfers            |    |

| 8.4 Requirements for P_CRCA during information unit transfers   |    |

| 8.5 Signal states                                               |    |

| 8.5.1 SE signals                                                |    |

| 8.5.2 LVD signals                                               |    |

| 8.6 OR-tied signals                                             |    |

| 8.7 Signal sources                                              |    |

| •                                                               |    |

| 9 SCSI parallel bus timing                                      | 83 |

| 9.1 SCSI parallel bus timing values                             | 83 |

| 9.2 Timing description                                          |    |

| 9.2.1 Arbitration delay                                         |    |

| 9.2.2 ATN transmit setup time                                   |    |

| 9.2.3 ATN receive setup time                                    |    |

| 9.2.4 Bus clear delay                                           |    |

| 9.2.5 Bus free delay                                            |    |

| 9.2.6 Bus set delay                                             |    |

| 9.2.7 Bus settle delay                                          |    |

| 9.2.8 Cable skew                                                |    |

| 9.2.9 pCRC Receive hold time                                    |    |

| 9.2.10 pCRC Receive setup time                                  |    |

| 9.2.11 pCRC Transmit hold time                                  |    |

| 9.2.12 pCRC Transmit setup time                                 |    |

| 9.2.14 DIFFSENS voltage filter time                             |    |

| 9.2.15 Physical disconnection delay                             |    |

| 0.2. 10 1 hydical didoonii collon dolay                         | 01 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 9.2.17 QAS arbitration delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                  |

| 9.2.18 QAS assertion delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                  |

| 9.2.19 QAS release delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                     |

| 9.2.20 QAS non-DATA phase REQ (ACK) period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 87                                  |

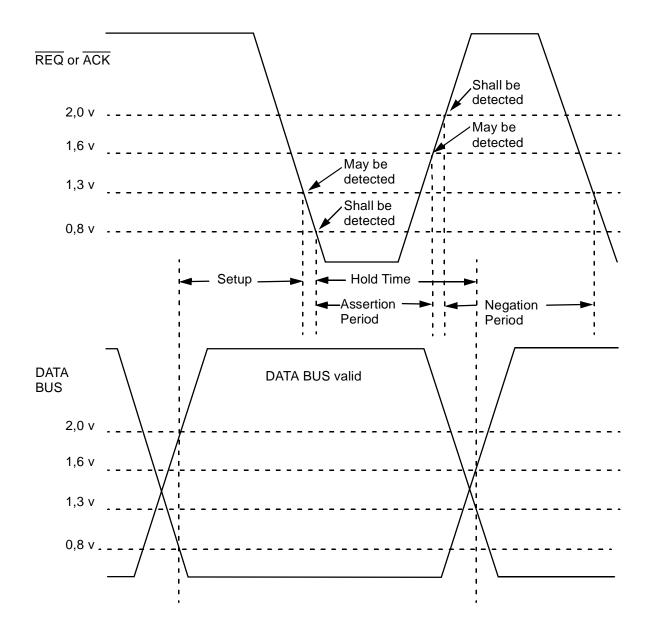

| 9.2.21 Receive assertion period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |

| 9.2.22 Receive hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 88                                  |

| 9.2.23 Receive negation period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88                                  |

| 9.2.24 Receive setup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                     |

| 9.2.25 Receive REQ (ACK) period tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                  |

| 9.2.26 REQ (ACK) period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 88                                  |

| 9.2.27 Reset delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88                                  |

| 9.2.28 Reset hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 88                                  |

| 9.2.29 Reset to selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                  |

| 9.2.30 Selection abort time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88                                  |

| 9.2.31 Selection time-out delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89                                  |

| 9.2.32 Signal Timing Skew                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89                                  |

| 9.2.33 System deskew delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 89                                  |

| 9.2.34 Transmit assertion period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                     |

| 9.2.35 Transmit hold time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 89                                  |

| 9.2.36 Transmit negation period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 89                                  |

| 9.2.37 Transmit setup time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 89                                  |

| 9.2.38 Transmit REQ (ACK) period tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 89                                  |

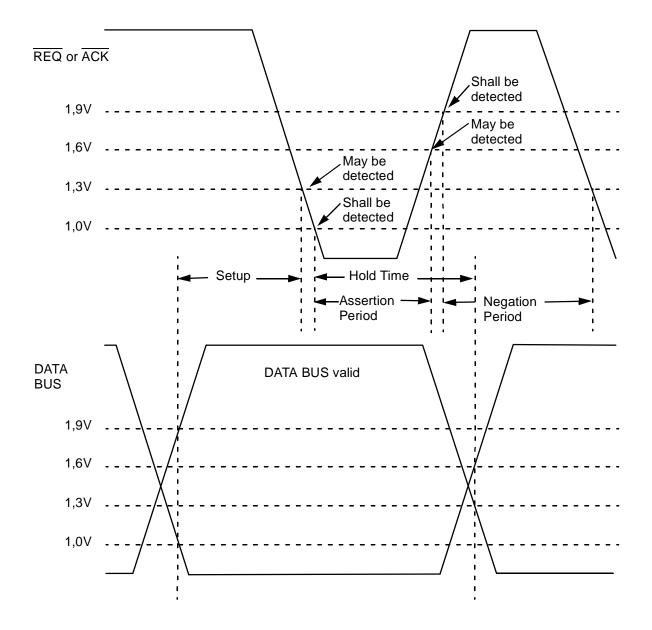

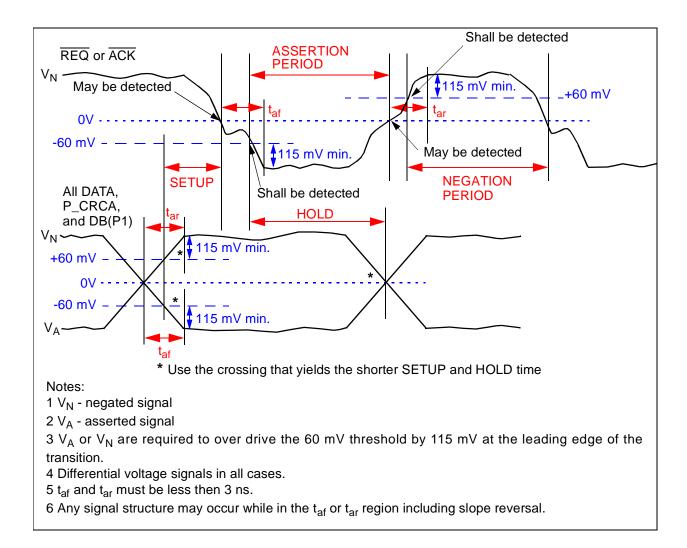

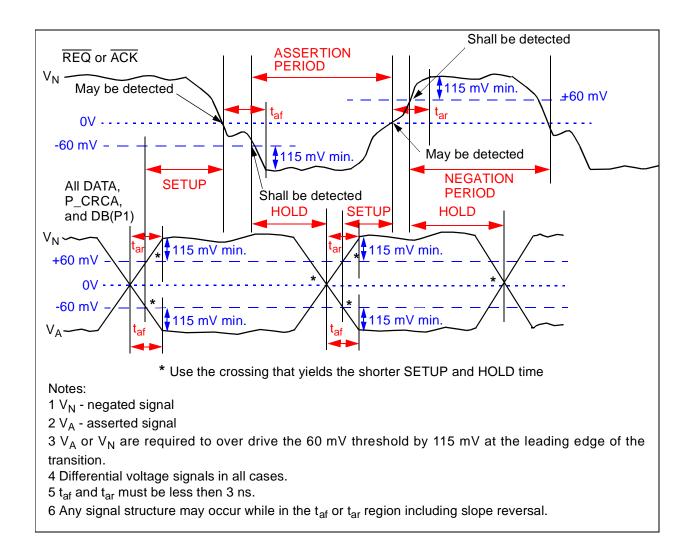

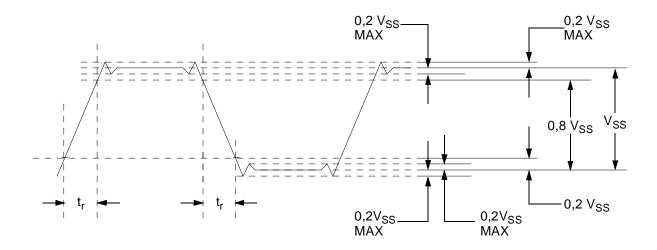

| 9.3 Measurement points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 89                                  |

| 9.3.1 SE fast-5 and fast-10 data transfer rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |

| 9.3.2 SE fast-20 data transfer rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90                                  |

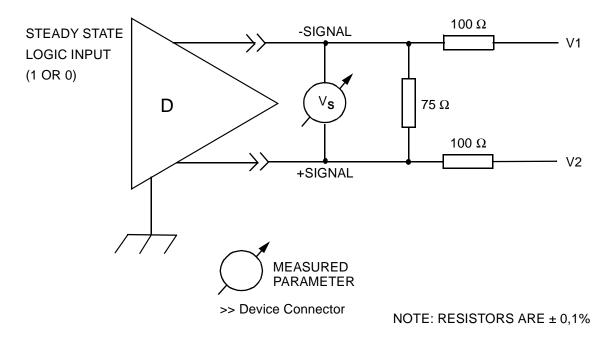

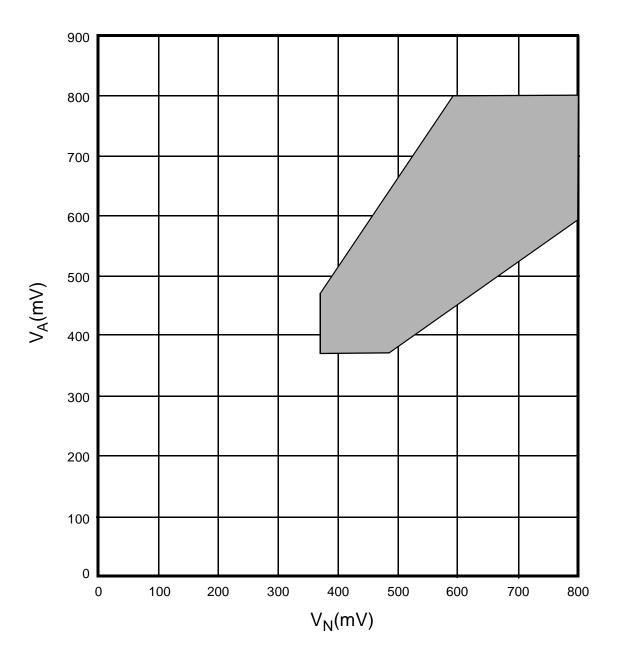

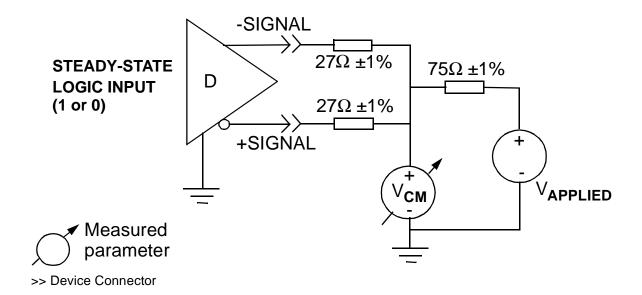

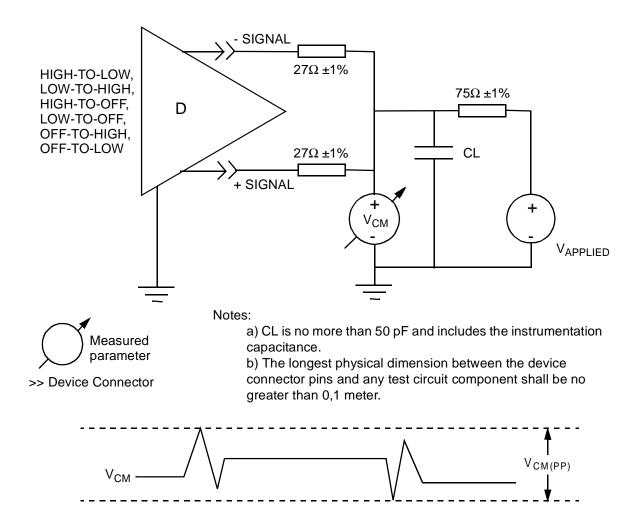

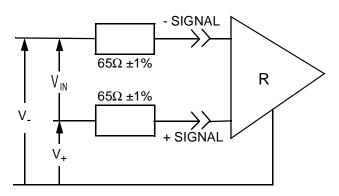

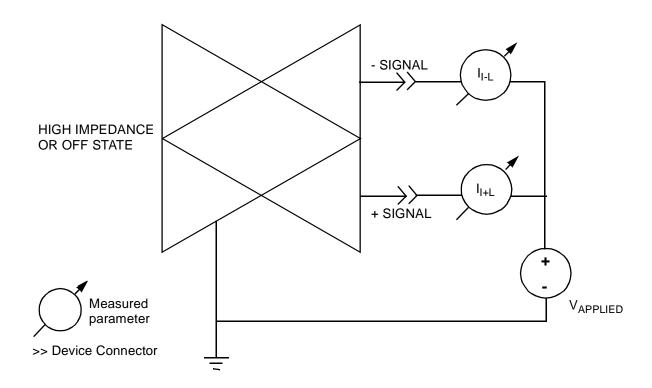

| 9.3.3 LVD data transfer rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91                                  |

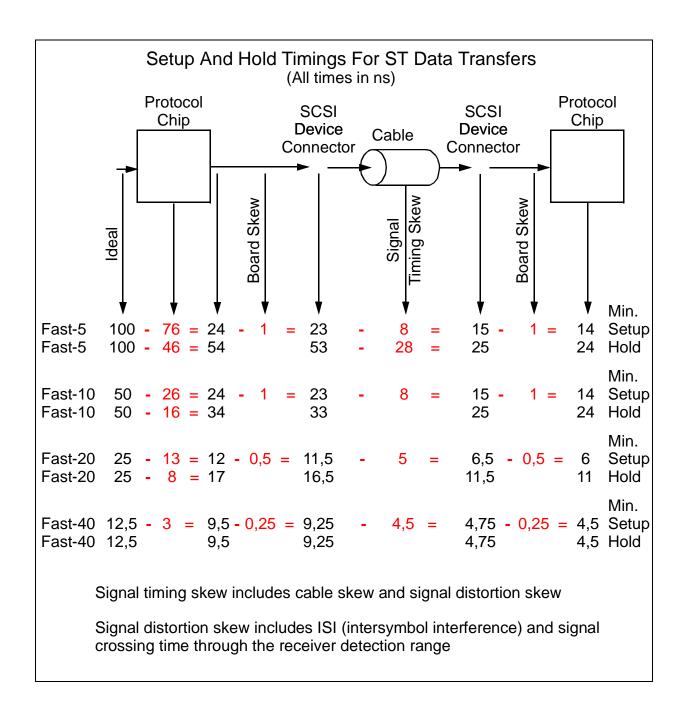

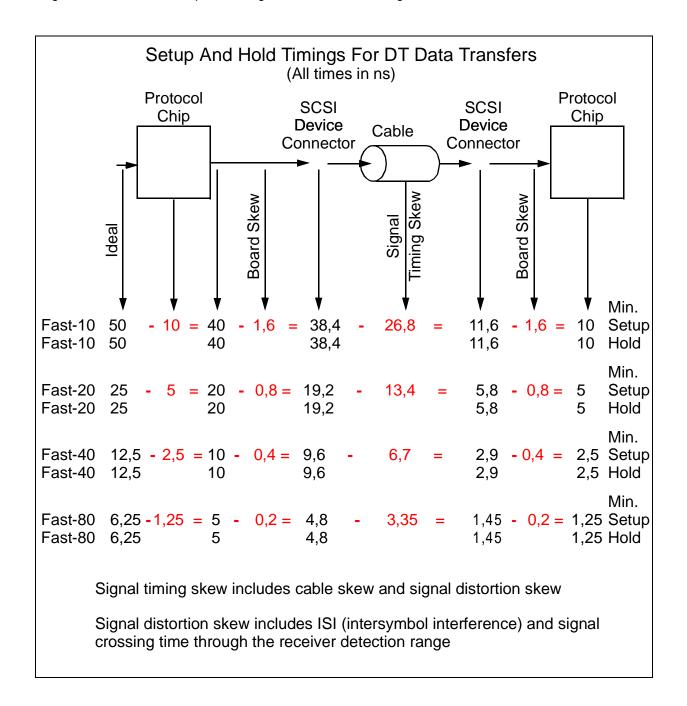

| 9.4 Setup and hold timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 93                                  |

| 9.4.1 ST data transfer calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 93                                  |

| 9.4.2 DT data transfer calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 95                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                     |

| 10 SCSI bus phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     |

| 10.1 BUS FREE phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97                                  |

| 10.1 BUS FREE phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97                                  |

| 10.1 BUS FREE phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97<br>97                            |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97<br>98<br>98                      |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97<br>98<br>98                      |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97<br>98<br>98<br>99                |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 97<br>98<br>98<br>99                |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97989899100101                      |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97989899100101101                   |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 979899100101101                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 979899100101101101                  |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 979898100101101101101               |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 97989899100101101101101102          |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Selection using attention condition 10.3.1.1.1 Information unit transfers disabled 10.3.1.2 Information unit transfers enabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 97989899100101101101101102102       |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Selection using attention condition 10.3.1.2 Information unit transfers disabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97989899101101101101102102          |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Selection using attention condition 10.3.1.2 Information unit transfers disabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 97989899100101101101102102103       |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Information unit transfers disabled 10.3.1.2 Information unit transfers enabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.3.1.2.1 Selection without using attention condition time-out procedure 10.4 RESELECTION phase 10.4.1 Physical reconnection 10.4.1.1 Physical reconnection time-out procedure                                                                                                                                                                                                                                                             |                                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Selection using attention condition 10.3.1.1.1 Information unit transfers disabled 10.3.1.2 Information unit transfers enabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.3.1.2.1 Selection without using attention condition 10.3.1.2.1 Physical reconnection 10.4.1 Physical reconnection 10.4.1.1 Physical reconnection time-out procedure                                                                                                                                                                                                                                                                            |                                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Selection using attention condition 10.3.1.2 Information unit transfers disabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.3.1.2.1 Selection without using attention condition 10.4.1 Physical reconnection 10.4.1 Physical reconnection time-out procedure 10.5 Information transfer phases 10.5.1 Asynchronous information transfer                                                         |                                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Information unit transfers disabled 10.3.1.2 Information unit transfers enabled 10.3.1.2 Information unit transfers enabled 10.3.1.2 Selection without using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.1.1 Physical reconnection 10.4.1 Physical reconnection 10.4.1.1 Physical reconnection time-out procedure 10.5 Information transfer phases 10.5.1 Asynchronous information transfer 10.5.2 Synchronous data transfer                                                                                                                                                                                                                                                                        | 97989899101101101102102103104104105 |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.2 Selection using attention condition 10.3.1.1 Information unit transfers disabled 10.3.1.1.2 Information unit transfers enabled 10.3.1.2 Selection without using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.1 Selection without using attention condition 10.3.1.1 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.3.1.2.1 Selection without using attention condition time-out procedure 10.4 RESELECTION phase 10.4.1 Physical reconnection 10.4.1.1 Physical reconnection 10.5.1 Asynchronous information transfer 10.5.2 Synchronous data transfer 10.5.2 Synchronous data transfer                                                         |                                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Information unit transfers disabled 10.3.1.1.2 Information unit transfers enabled 10.3.1.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition time-out procedure 10.3.1.2 Selection without using attention condition 10.3.1.1.1 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.4.1.2 Negration without using attention condition time-out procedure 10.4 RESELECTION phase 10.4.1 Physical reconnection 10.4.1.1 Physical reconnection 10.4.1.1 Physical reconnection time-out procedure 10.5 Information transfer phases 10.5.1 Asynchronous information transfer 10.5.2 Synchronous data transfer 10.5.2.3 DT synchronous data transfer |                                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Information unit transfers disabled 10.3.1.2 Information unit transfers enabled 10.3.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition time-out procedure 10.3.1.1 Selection without using attention condition 10.3.1.2 Information unit transfers enabled 10.3.1.3 Selection without using attention condition 10.4.1.1 Physical reconnection time-out procedure 10.4 RESELECTION phase 10.4.1 Physical reconnection 10.5.1 Information transfer phases 10.5.1 Asynchronous information transfer 10.5.2 Synchronous data transfer 10.5.2.2 DT synchronous data transfer 10.5.2.2 DT synchronous data transfer                                                                               |                                     |

| 10.1 BUS FREE phase 10.1.1 Unexpected and expected bus free 10.2 Arbitration 10.2.1 NORMAL ARBITRATION phase 10.2.2 QAS protocol 10.2.2.1 QAS phase 10.3 SELECTION phase 10.3.1 Selection 10.3.1.1 Information unit transfers disabled 10.3.1.1.2 Information unit transfers enabled 10.3.1.1.3 Selection using attention condition time-out procedure 10.3.1.2 Selection without using attention condition time-out procedure 10.3.1.1 Selection without using attention condition 10.3.1.1.1 Selection without using attention condition 10.3.1.2 Selection without using attention condition 10.4.1.2 Information transfer phase 10.4.1 Physical reconnection 10.4.1.1 Physical reconnection time-out procedure 10.5 Information transfer phases 10.5.1 Asynchronous information transfer 10.5.2 Synchronous data transfer 10.5.2.1 ST synchronous data transfer                                                                                           |                                     |

| 10.5.2.2.2 Data Group data field transfer                                                           | 108 |

|-----------------------------------------------------------------------------------------------------|-----|

| 10.5.2.2.2.1 Data Group Pad field and pCRC field transfer to initiator                              |     |

| 10.5.2.2.2 Data Group Pad field and pCRC field transfer to target                                   |     |

| 10.5.2.3 Wide data transfer                                                                         |     |

| 10.6 COMMAND phase                                                                                  |     |

| 10.6.1 Command phase exception condition handling                                                   |     |

| 10.7 DATA phase                                                                                     |     |

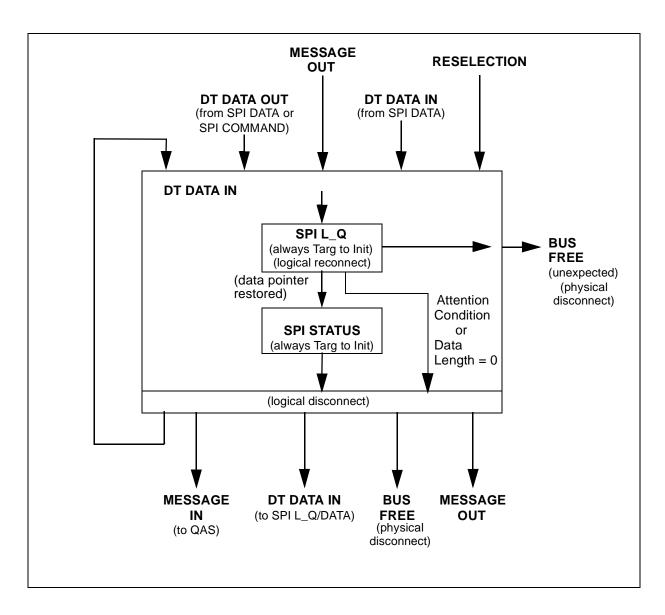

| 10.7.1 DT DATA IN phase                                                                             | 113 |

| 10.7.2 DT DATA OUT phase                                                                            | 113 |

| 10.7.3 ST DATA IN phase                                                                             | 113 |

| 10.7.4 ST DATA OUT phase                                                                            | 113 |

| 10.8 STATUS phase                                                                                   |     |

| 10.8.1 STATUS phase exception condition handling                                                    | 113 |

| 10.9 MESSAGE phase                                                                                  | 113 |

| 10.9.1 MESSAGE IN phase                                                                             | 114 |

| 10.9.1.1 MESSAGE IN phase exception condition handling                                              |     |

| 10.9.2 MESSAGE OUT phase                                                                            |     |

| 10.9.2.1 MESSAGE OUT phase exception condition handling                                             |     |

| 10.10 Signal restrictions between phases                                                            | 115 |

|                                                                                                     |     |

| 11 Data bus protection                                                                              |     |

| 11.1 ST data bus protection (parity checking rules)                                                 |     |

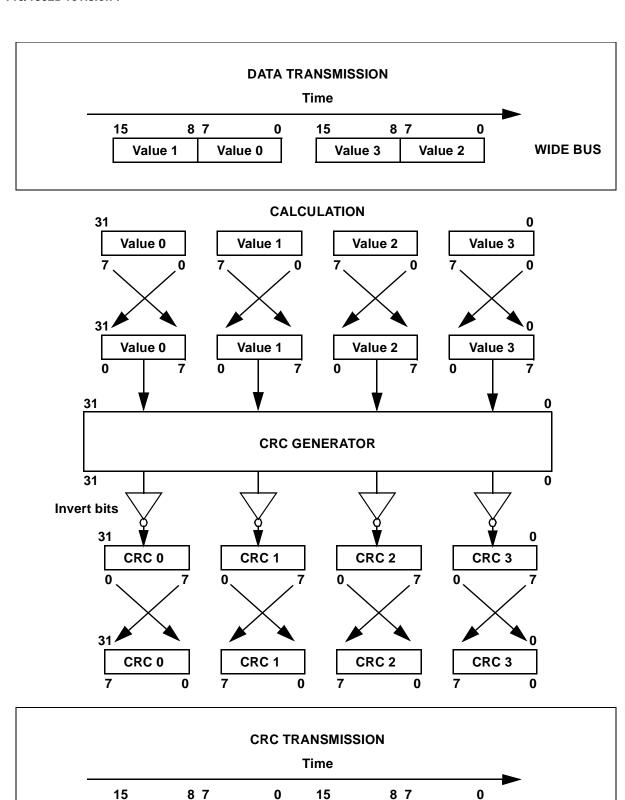

| 11.2 DT data bus protection (CRC)                                                                   |     |

| 11.2.1 Error detection capabilities                                                                 |     |

| 11.2.2 Order of bytes in the CRC field                                                              |     |

| 11.2.3 CRC generation and checking                                                                  |     |

| 11.2.4 Test cases                                                                                   | 119 |

|                                                                                                     |     |

| 12 SCSI bus conditions                                                                              |     |

| 12.1 Attention condition                                                                            |     |

| 12.2 Hard reset                                                                                     |     |

| 12.3 Reset events                                                                                   |     |

| 12.3.1 Transceiver mode change reset event                                                          | 121 |

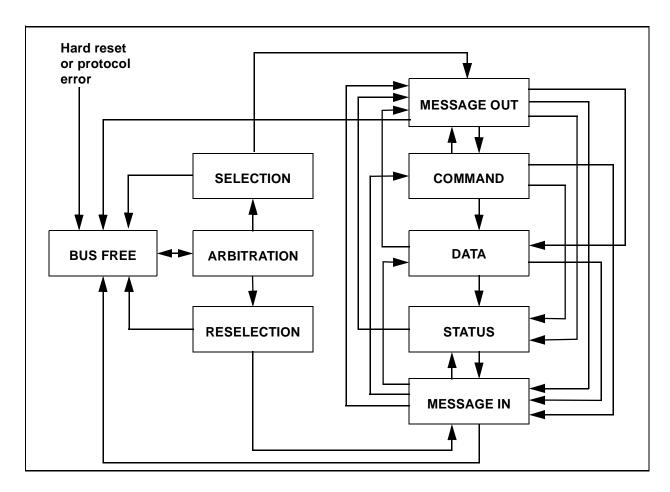

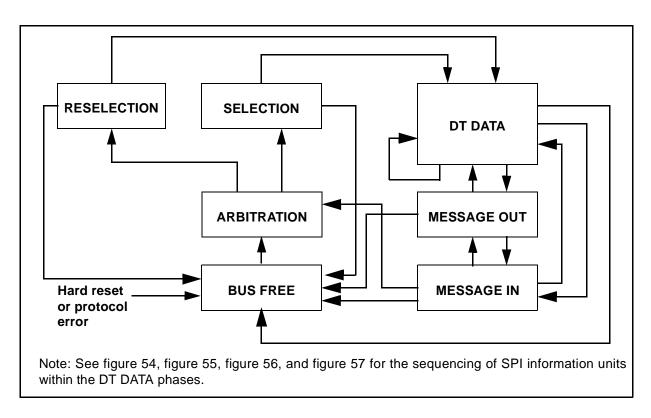

| 13 SCSI bus phase sequences                                                                         | 122 |

| 13.1 Phase sequences for physical reconnection and selection using attention condition with info    |     |

| tion unit transfers disabled                                                                        |     |

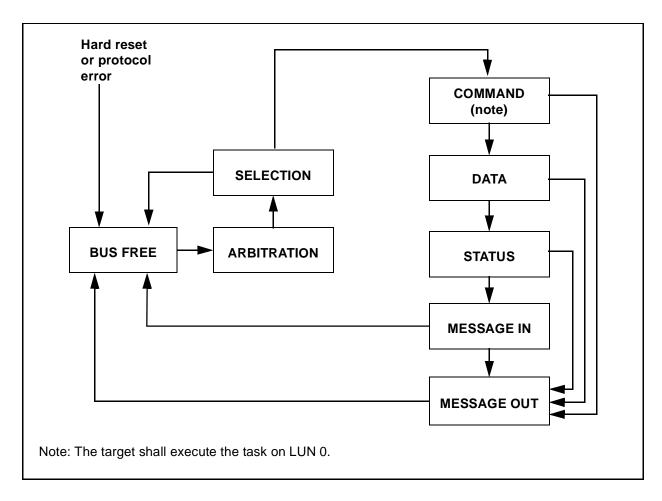

| 13.2 Phase sequences for selection without using attention condition with information unit transfer |     |

| abled                                                                                               |     |

| 13.3 Phase sequences for selection without using attention condition/physical reconnection with     |     |

| mation unit transfers enabled                                                                       |     |

| mation that transfers enabled                                                                       | 120 |

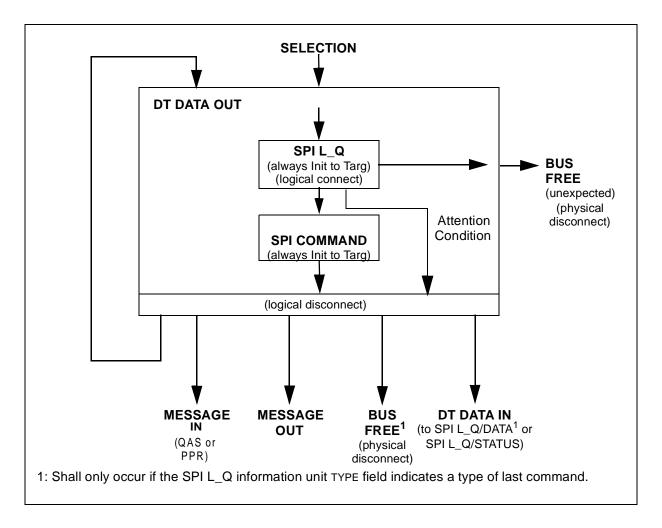

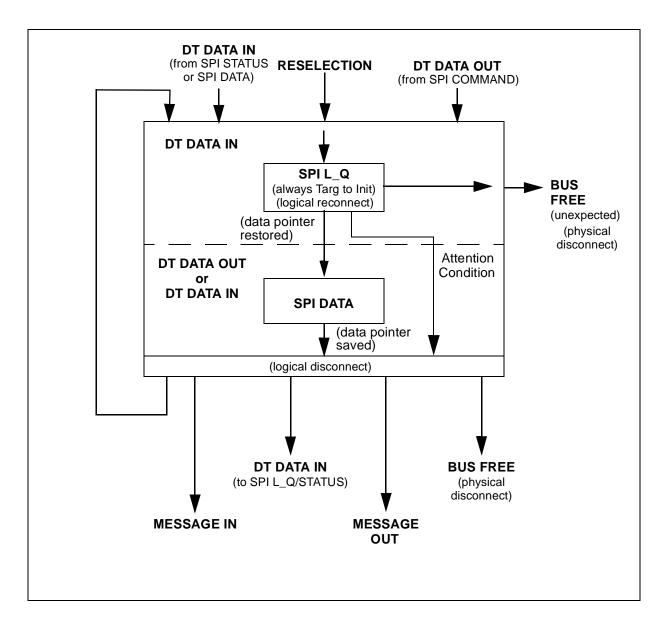

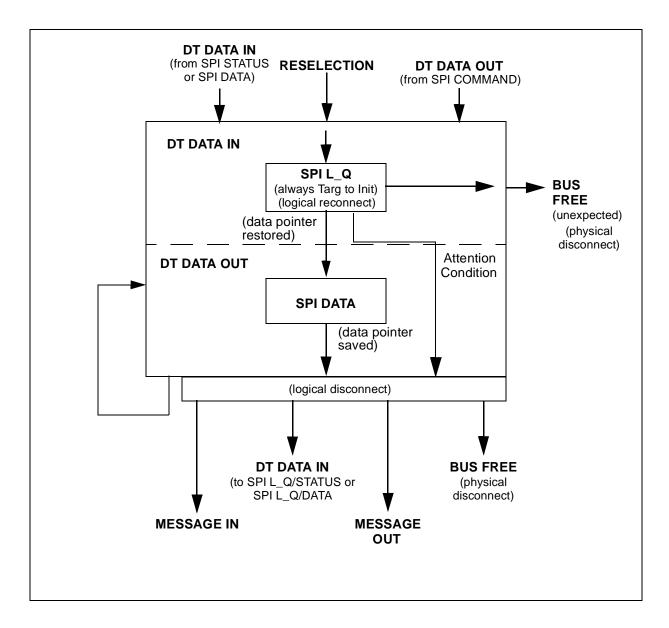

| 14 SPI information unit sequences                                                                   | 127 |

| 14.1 Information unit transfer logical operations                                                   | 127 |

| 14.2 SPI information units                                                                          |     |

| 14.2.1 SPI command information unit                                                                 | 132 |

| 14.2.2 SPI L_Q information unit                                                                     |     |

| 14.2.3 SPI data information unit                                                                    |     |

| 14.2.4 SPI data stream information unit                                                             |     |

| 14.2.5 SPI status information unit                                                                  |     |

|                                                                                                     |     |

| 15 SCSI pointers                                                                                    | 141 |

| •                                                                                                   | • • |

| 16 SCSI Protocol messages                                                                           | 142 |

| 16.1 Message protocols and formats                                                                  |     |

| 16.1.1 Message protocol rules                                                                       |     |

| 16.1.2 Message formats                                                                              | 142 |

| 16.1.2.1 One-byte messages                                         | 143 |

|--------------------------------------------------------------------|-----|

| 16.1.2.2 Two-byte messages                                         |     |

| 16.1.2.3 Extended messages                                         |     |

| 16.2 Link control messages                                         |     |

| 16.2.1 DISCONNECT                                                  |     |

| 16.2.2 IDENTIFY                                                    | 146 |

| 16.2.3 IGNORE WIDE RESIDUE                                         | 147 |

| 16.2.4 INITIATOR DETECTED ERROR                                    | 148 |

| 16.2.5 MESSAGE PARITY ERROR                                        | 148 |

| 16.2.6 MESSAGE REJECT                                              | 148 |

| 16.2.7 MODIFY DATA POINTER                                         | 149 |

| 16.2.8 NO OPERATION                                                |     |

| 16.2.9 PARALLEL PROTOCOL REQUEST                                   |     |

| 16.2.9.1 Target initiated PARALLEL PROTOCOL REQUEST negotiation    |     |

| 16.2.9.2 Initiator initiated PARALLEL PROTOCOL REQUEST negotiation |     |

| 16.2.10 QAS REQUEST                                                |     |

| 16.2.11 RESTORE POINTERS                                           |     |

| 16.2.12 SAVE DATA POINTER                                          |     |

| 16.2.13 SYNCHRONOUS DATA TRANSFER REQUEST                          |     |

| 16.2.13.1 Target initiated SDTR negotiation                        |     |

| 16.2.13.2 Initiator initiated SDTR negotiation                     |     |

| 16.2.14 TASK COMPLETE                                              |     |

| 16.2.15 WIDE DATA TRANSFER REQUEST                                 |     |

| 16.2.15.1 Target initiated WDTR negotiation                        |     |

| 16.2.15.2 Initiator initiated WDTR negotiation                     |     |

| 16.3 Task attribute messages                                       |     |

| 16.3.1 ACA                                                         |     |

| 16.3.2 HEAD OF QUEUE                                               |     |

| 16.3.3 LINKED COMMAND COMPLETE                                     |     |

| 16.3.4 ORDERED                                                     |     |

| 16.3.5 SIMPLE                                                      |     |

| 16.3.6 Task management messages                                    |     |

| 16.3.7 ABORT TASK                                                  |     |

| 16.3.8 ABORT TASK SET                                              |     |

| 16.3.9 CLEAR ACA                                                   |     |

| 16.3.10 CLEAR TASK SET                                             |     |

| 16.3.11 LOGICAL UNIT RESET                                         |     |

| 16.3.12 TARGET RESET                                               | 167 |

| 17 Command pressessing considerations and expention conditions     | 160 |

| 17 Command processing considerations and exception conditions      | 160 |

| 17.1 Asynchronous event notification                               |     |

| 17.3 Unexpected RESELECTION phase                                  |     |

| 17.5 Offexpected NEGLECTION priase                                 | 103 |

| 18 SCSI management features for the SCSI parallel interface        | 170 |

| 18.1 SCSI mode parameters                                          |     |

| 18.1.1 Disconnect-reconnect mode page                              |     |

| 18.1.2 Logical Unit Control mode page                              |     |

| 18.1.3 Port Control mode page                                      |     |

| 10.1.0 1 of Control Mode page                                      | 17  |

| 19 SCSI parallel interface services                                | 175 |

| 19.1 Procedure terms                                               |     |

| 19.2 Application client SCSI command services                      |     |

| 19.2.1 Send SCSI command service                                   |     |

| 19.3 Device server SCSI command services                           |     |

| 19.3.1 Data-in delivery service                                    |     |

| 19.3.2 Data-out delivery service                                   |     |

| 19.4 Task management services                                              | 178 |

|----------------------------------------------------------------------------|-----|

| 19.4.1 Task management function service                                    | 178 |